Background & Motivation

As semiconductor packages become increasingly complex, design decisions

must consider multi-physics reliability constraints from the earliest

design stages. However, conventional design flows rely heavily on

manual modeling and repetitive simulations, leading to long development

cycles and limited design exploration.

To overcome these limitations, our research focuses on building

virtual design environments that automate simulation setup, integrate

reliability metrics, and enable systematic design optimization.

Current Research Projects

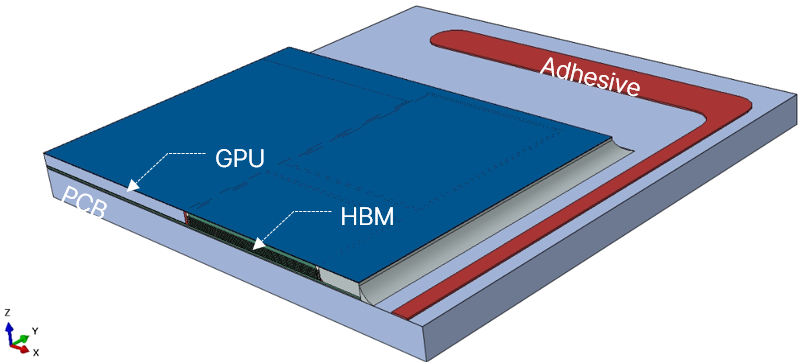

Package Structure Design Optimization

Development of automated modeling and simulation workflows that reflect circuit layouts, material stacks, and structural design variables. The framework enables rapid evaluation of warpage, stress, and deformation during package design optimization.

Board-Level Reliability Prediction Automation

Construction of a virtual environment for real-time prediction of board-level reliability, including BLR metrics such as thermal cycling, drop, and mechanical loading. The system automates simulation execution, result extraction, and reliability assessment.

Production-Oriented Optimization & Deployment

Deployment of the optimized design framework into production-oriented environments. The system enables rapid assessment of reliability impacts due to design changes and supports decision-making for cost reduction and development cycle acceleration.

Methodology

- Automated generation of simulation-ready package and board models

- Integration of reliability metrics into design optimization loops

- Virtual environments for rapid design iteration and evaluation

Key Results & Impact

The proposed virtual design environments significantly reduce development time by minimizing manual modeling effort and enabling early-stage reliability evaluation. These tools support systematic design optimization and have been successfully applied to advanced package and board-level reliability problems.